The University of Manchester

The University of Manchester Research

# Charge-trapping memory based on tri-layer alumina gate stack and InGaZnO channel

### DOI:

10.1088/1361-6641/ab7c7a

## **Document Version**

Accepted author manuscript

Link to publication record in Manchester Research Explorer

Citation for published version (APA):

Ma, P., Gao, J., Guo, W., Zhang, G., Whang, Y., Xin, Q., Li, Y., & Song, A. (2020). Charge-trapping memory based on tri-layer alumina gate stack and InGaZnO channel. *Semiconductor Science and Technology*, *35*, Article 055032. https://doi.org/10.1088/1361-6641/ab7c7a

#### Published in:

Semiconductor Science and Technology

Citing this paper

Please note that where the full-text provided on Manchester Research Explorer is the Author Accepted Manuscript or Proof version this may differ from the final Published version. If citing, it is advised that you check and use the publisher's definitive version.

General rights

Copyright and moral rights for the publications made accessible in the Research Explorer are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

Takedown policy

If you believe that this document breaches copyright please refer to the University of Manchester's Takedown Procedures [http://man.ac.uk/04Y6Bo] or contact openresearch@manchester.ac.uk providing relevant details, so we can investigate your claim.

Charge-trapping memory based on tri-layer alumina gate

stack and InGaZnO channel

Pengfei Ma,† Jiacheng Gao,† Wenhao Guo,† Guanqun Zhang,† Yiming Wang,† Qian Xin,† Yuxiang

Li,\*,† and Aimin Song\*,†,‡,§

†Center of Nanoelectronics and School of Microelectronics, Shandong University, Jinan 250100, China

‡State Key Laboratory of Crystal Materials, Shandong University, Jinan 250100, China

§School of Electrical and Electronic Engineering, University of Manchester, Manchester M13 9PL, United Kingdom

Pengfei Ma and Jiacheng Gao are co-first authors.

**ABSTRACT**

Amorphous InGaZnO (IGZO) charge-trapping memory (CTM) devices have been designed and

demonstrated entirely with thin-film technologies. All three key layers for blocking, charge-

trapping, and tunneling in gate stack are made by Al<sub>2</sub>O<sub>3</sub> grown by atomic-layer deposition but with

different oxygen sources, i.e., O<sub>3</sub> or deionized H<sub>2</sub>O, to achieve different properties. X-ray

photoelectron spectroscopy reveals that few defects exist in the H<sub>2</sub>O-Al<sub>2</sub>O<sub>3</sub> film with only Al-O

bonding, while more residual C-related impurities appear in the O<sub>3</sub>-Al<sub>2</sub>O<sub>3</sub> film leading to a high

density of defects, which serve as the charge-trapping states in the gate stack of the CTM devices.

The fabricated IGZO CTM can be programmed under a positive voltage bias, and a large memory

window of 8.2 V can be obtained with a programming voltage of +20 V. Multi-level storage has

been achieved in the fabricated IGZO CTM, and a 1.9 V wide margin between the adjacent two

states could be maintained for more than 10 years according to the trend of the data. With light

illumination, the memory device can be erased entirely under a negative bias of -5 V. The IGZO

CTM devices may have promising potentials for multi-level-storage nonvolatile memory

applications based on thin-film technologies.

**KEYWORDS:** Charge-trapping memory, Al<sub>2</sub>O<sub>3</sub>, O<sub>3</sub>, InGaZnO, Multi-level storage

1

## 1. INTRODUCTION

Traditional flash memories are suffering from the miniaturization limit due to high integration density, reliability, and lithography techniques. Since the first three-dimensional (3D) NAND array was proposed in 2007 by Toshiba corporation,<sup>2</sup> alternative methods to improve the storage capacity are pursued by major memory manufacturers, resulting in the first commercial product in Samsung Electronics until 2013.<sup>3</sup> Charge-trapping memory (CTM) based on SiO<sub>2</sub>/Si<sub>3</sub>N<sub>4</sub>/SiO<sub>2</sub> (ONO) gate stack structure is the key element of 3D NAND.<sup>2</sup> However, the CTM devices suffer from quick charge loss due to charge detrapping through the thin tunneling layer. Fortunately, the suppression of tunneling current can be realized by using thick high-k dielectric films, which are prospective for substituting the traditional ONO gate stack to realize large memory window, low operation voltage, and high program and erase speed.<sup>4</sup> Among the well-known high-k materials, Al<sub>2</sub>O<sub>3</sub> is a very promising candidate due to the high dielectric constant  $(k \sim 9.0)$  and the relatively high band gap  $(E_g \sim 8 \text{ eV})^{.5}$  In our previous work, Al<sub>2</sub>O<sub>3</sub> film grown by atomic-layer deposition (ALD) has been demonstrated to be a highly reliable gate insulator. Furthermore, Al<sub>2</sub>O<sub>3</sub> has been investigated as tunneling/blocking layers in the CTM devices, due to the superior thermal and chemical stability and the strong adhesion to dissimilar materials.<sup>1,7</sup> Al<sub>2</sub>O<sub>3</sub> was also proposed to be used as the charge-trapping layer in the CTM devices, which showed good retention characteristics, but a small memory window caused by the low trap density.<sup>4</sup> Doping different elements, such as Ta, 8 Ti, 9 and Hf, 10 into Al<sub>2</sub>O<sub>3</sub> layer could increase the trap density and the memory window. Shallow traps in these films lead to a poor retention performance. However, large memory window and reliable retention characteristics are crucial for multi-level-storage memory. Researchers have reported the effects of different ALD oxygen sources (H<sub>2</sub>O, H<sub>2</sub>O<sub>2</sub>, and O<sub>3</sub>) on Al<sub>2</sub>O<sub>3</sub> films during the deposition, and found that H<sub>2</sub>O has ideal ligand exchange reactions with trimethylaluminum (TMA), while O<sub>3</sub> leads to a high density of impurities in the film under a low growth temperature. <sup>11</sup>, <sup>12</sup> By using different oxygen sources, defect-rich and few-defect dielectric Al<sub>2</sub>O<sub>3</sub> layers could be achieved, which can act as charge-trapping and tunneling/blocking layers, respectively.

With increasing the number of 3D NAND gate stack layers, a small cell current with large fluctuation originating from grain and/or interfacial traps in the traditional poly-silicon (poly-Si) channel material is a severe problem. 13-15 It's essential to find new channel materials to meet the 3D memory demand. Amorphous InGaZnO (IGZO) first proposed by Hosono et al. in 2004 has been widely studied due to its excellent characteristics, including high electron mobility, low off current, large-area mass-production compatibility, and low process temperatures. 16 In our previous works, we have also proposed the low power applications of IGZO TFTs based on various high-κ dielectric layers. 6,17,18 As a promising channel material, low-temperature-fabricated IGZO was also reported to be used in the CTM devices, which may be applied in flexible and wearable electronics. 19-24 During the manufacturing process of 3D NAND devices, conformal characteristics of films are quite important. Highly conformal films can be achieved by ALD and sputtering technologies, which allow precise thickness control. Recently, high-performance ALD-grown IGZO thin-film transistors (TFTs) have been realized, which means that IGZO can satisfy 3D manufacturing processes. 25

In this work, the memory characteristics of the CTM devices based on triple-layer ALD-alumina gate stack and IGZO channel layer have been systemically investigated. To achieve excellent non-volatile memory (NVM) properties, low-defect Al<sub>2</sub>O<sub>3</sub> films grown with TMA and deionized H<sub>2</sub>O (denoted as H<sub>2</sub>O-Al<sub>2</sub>O<sub>3</sub>) were used as blocking and tunneling layers, meanwhile the defect-rich Al<sub>2</sub>O<sub>3</sub> film grown by substituting O<sub>3</sub> for deionized H<sub>2</sub>O as the oxygen source (denoted as O<sub>3</sub>-Al<sub>2</sub>O<sub>3</sub>) was used as the charge-trapping layer. The defects in O<sub>3</sub>-Al<sub>2</sub>O<sub>3</sub> film were identified through X-ray photoelectron spectroscopy (XPS) measurements. Al/Al<sub>2</sub>O<sub>3</sub>/n-Si (MOS) capacitors were also fabricated to determine the trap densities in H<sub>2</sub>O-Al<sub>2</sub>O<sub>3</sub> and O<sub>3</sub>-Al<sub>2</sub>O<sub>3</sub> layers. The achieved IGZO CTM devices showed multi-level storage with a good reliability, which have a great promise for the future nonvolatile memory applications.

## 2. EXPERIMENTAL SECTION

First, bottom gate electrodes with 5 nm Ti and 30 nm Au layers were deposited on a cleaned Si/SiO<sub>2</sub> substrate by electron-beam evaporation. For the CTM devices, 15, 10, and 5 nm Al<sub>2</sub>O<sub>3</sub> layers were grown on the gate electrodes by ALD at a low temperature of 150 °C successively, serving as blocking, charge-trapping, and tunneling layers, respectively. Deionized H<sub>2</sub>O and TMA were used in the growth of blocking and tunneling layers. During the charge-trapping layer growth, O<sub>3</sub> substituted for deionized H<sub>2</sub>O as the oxygen source. During the homogeneous tri-layers Al<sub>2</sub>O<sub>3</sub> growth, the dose time of TMA, H<sub>2</sub>O and O<sub>3</sub> was 0.03 s, 0.015 s, and 5 s, respectively. There is a 30 s purge process after every dose operation. The precursors were carried by high purity N<sub>2</sub> gas and introduced to the reactor chamber with a chamber pressure of 0.15 Torr. To verify the chargetrapping performance of the CTM devices, the control samples (TFTs) based on 30 nm H<sub>2</sub>O-Al<sub>2</sub>O<sub>3</sub> film were also prepared. The 24 nm IGZO layer was deposited by radio-frequency (RF) sputtering at room temperature with a 90 W sputtering power under a 3.70 mTorr pressure. Ti source/drain electrodes were then deposited by electron-beam evaporation. The length and width of active channels were both 10 µm. The channel and electrodes were all patterned by photolithography. The trap densities in the Al<sub>2</sub>O<sub>3</sub> layer grown under different conditions were explored by fabrication of Al/Al<sub>2</sub>O<sub>3</sub>/n-Si capacitors. These devices were characterized by the capacitance-voltage (C-V) and current-voltage (I-V) measurements using the Keysight Technologies B1500A semiconductor device analyzer. Two types of Al<sub>2</sub>O<sub>3</sub> films were also examined by XPS after Ar<sup>+</sup> ion etching with ThermoFisher ESCALAB 250XI equipment.

## 3. RESULTS AND DISCUSSION

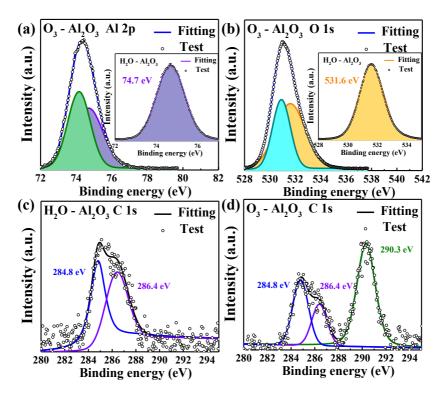

**Figure 1.** (a) Al 2p, (b) O 1 s core levels for O<sub>3</sub>-Al<sub>2</sub>O<sub>3</sub> film (main graph) and H<sub>2</sub>O-Al<sub>2</sub>O<sub>3</sub> (inset). C 1 s core levels for (c) H<sub>2</sub>O-Al<sub>2</sub>O<sub>3</sub> film and (d) O<sub>3</sub>-Al<sub>2</sub>O<sub>3</sub>, respectively.

The narrow-scan XPS spectra of Al 2p and O 1s of Al<sub>2</sub>O<sub>3</sub> films are shown in Figs. 1(a) and 1(b), respectively. All the XPS spectra were calibrated with C 1s peak of 284.8 eV. For H<sub>2</sub>O-Al<sub>2</sub>O<sub>3</sub> film, core level spectra of Al 2p and O 1s were fitted well as a symmetrical single peak at 74.7 eV and 531.6 eV for Al-O bonds, respectively. Besides the above peaks, additional peaks at 74.2 eV for Al 2p and at 530.9 eV for O 1s have been detected, respectively, in O<sub>3</sub>-Al<sub>2</sub>O<sub>3</sub> film. During the ALD processes, ideal ligand exchange can be accomplished between H<sub>2</sub>O and TMA even at a low growth temperature.<sup>5</sup> However, O<sub>3</sub> eliminates the ligands in TMA molecule by oxidation of the ligands, which needs to overcome a high reaction barrier.<sup>26, 27</sup> During the O<sub>3</sub>-Al<sub>2</sub>O<sub>3</sub> film growth, the imperfect ligand oxidation state may occur due to the low ALD growth temperature (150 °C). The peaks at 74.2 eV for Al 2p and at 530.9 eV for O 1s may originate from the different oxidation states in the film, such as Al-COOH and Al-OH species.<sup>11, 28</sup> What's more, various residual C-related impurities were also detected in O<sub>3</sub>-Al<sub>2</sub>O<sub>3</sub> film. Fig. 1(c) shows the C 1 s core level spectra for H<sub>2</sub>O-Al<sub>2</sub>O<sub>3</sub> film, which was combined with two peaks at 284.8 eV and 286.4 eV corresponding to C-C bonds resulting from the ambient and/or the pump oil vapor pollution in the XPS tool, and

the residual methyl from TMA, respectively. While, there was one more obvious peak at 290.3 eV in O<sub>3</sub>-Al<sub>2</sub>O<sub>3</sub> film, which could be caused by the C-related oxidation states, such as Al-CO<sub>3</sub> and Al-COOH, as shown in Fig. 1(d). These states at 290.3 eV in O<sub>3</sub>-Al<sub>2</sub>O<sub>3</sub> film may result from the slow decomposition of O<sub>3</sub> at low ALD growth temperature, which was almost disappeared in the XPS spectra after elevating the growth temperature (such as 250 °C, not shown here). The measured relative atomic percentage of C is about 0.9% and 2.2% for H<sub>2</sub>O-Al<sub>2</sub>O<sub>3</sub> and O<sub>3</sub>-Al<sub>2</sub>O<sub>3</sub>, respectively, which means there are more C-related impurities existed in O<sub>3</sub>-Al<sub>2</sub>O<sub>3</sub> leading to more traps in the film.

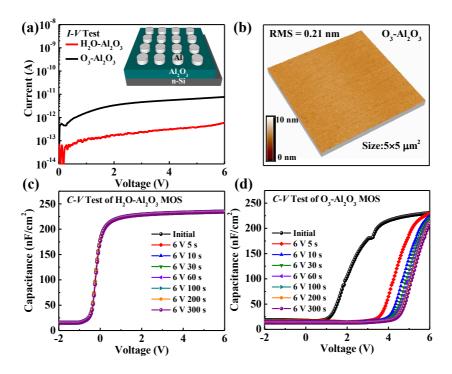

**Figure 2.** (a) *I-V* measurements (main graph) and schematic diagram (inset) of MOS capacitors based on 30 nm H<sub>2</sub>O-Al<sub>2</sub>O<sub>3</sub> and O<sub>3</sub>-Al<sub>2</sub>O<sub>3</sub> dielectrics. (b) AFM image of 30 nm O<sub>3</sub>-Al<sub>2</sub>O<sub>3</sub> layer grown on n-Si. *C-V* measurements with a constant 6 V bias stress of MOS devices based on 30 nm (c) H<sub>2</sub>O-Al<sub>2</sub>O<sub>3</sub> and (d) O<sub>3</sub>-Al<sub>2</sub>O<sub>3</sub> layers.

The dielectric characteristic and trap density of H<sub>2</sub>O-Al<sub>2</sub>O<sub>3</sub> and O<sub>3</sub>-Al<sub>2</sub>O<sub>3</sub> films were further investigated by fabricating Al/Al<sub>2</sub>O<sub>3</sub>/n-Si (MOS) devices. Fig. 2(a) shows the *I-V* measurements and the schematic diagram of the MOS capacitors based on 30 nm Al<sub>2</sub>O<sub>3</sub> films. As seen in Fig. 2(a), the leakage current through the O<sub>3</sub>-Al<sub>2</sub>O<sub>3</sub> film was founded to be more than one order of magnitude larger than that for the H<sub>2</sub>O-Al<sub>2</sub>O<sub>3</sub> film. As is well known, large surface roughness of film will result in the large leakage current. However, the O<sub>3</sub>-Al<sub>2</sub>O<sub>3</sub> film showed a smooth surface with the

root-mean-square (RMS) roughness of 0.21 nm, as shown in Fig. 2(b), which was very similar to our previous reported 0.28 nm roughness for H<sub>2</sub>O-Al<sub>2</sub>O<sub>3</sub> with the same film thickness.<sup>6</sup> Using O<sub>3</sub> as the oxygen source, the chemical reaction between TMA and O<sub>3</sub> may be incomplete, especially at a low temperature, which will lead to much C-related impurities in the Al<sub>2</sub>O<sub>3</sub> dielectric layer. <sup>11</sup> Thus, the large leakage current of O<sub>3</sub>-Al<sub>2</sub>O<sub>3</sub> may be ascribed to the more defects in the film rather than the film surface roughness. These defects could act as charge trapping centers in the film, and C-V measurements could be used to explore the charge trapping density through the flat band voltage shift ( $\Delta V_{\rm fb}$ ) after a constant voltage stress. The  $\Delta V_{\rm fb}$  after a 6 V voltage stress from 5 s to 300 s were showed in Figs. 2(c) and 2(d), and the density of trapped oxide charge  $(N_t)$  can be obtained from the  $\Delta V_{\rm fb}$  using the equation of  $N_{\rm t} = (C_{\rm max} \Delta V_{\rm fb})/qA$ , where  $C_{\rm max}$  is the maximal value of capacitance, and A is the electrode area. <sup>30</sup> After a 300 s constant bias stress, the C-V curves were slight changed for H<sub>2</sub>O-Al<sub>2</sub>O<sub>3</sub> device. However, there was a 2.32 V shift of V<sub>fb</sub> for O<sub>3</sub>-Al<sub>2</sub>O<sub>3</sub> capacitors. The calculated trap density for O<sub>3</sub>-Al<sub>2</sub>O<sub>3</sub> device is 3.62×10<sup>12</sup> cm<sup>-2</sup>, which is more than two order of magnitude higher than 1.83×10<sup>10</sup> cm<sup>-2</sup> for the H<sub>2</sub>O-Al<sub>2</sub>O<sub>3</sub> film. We also tested the retention characteristics of Al/O<sub>3</sub>-Al<sub>2</sub>O<sub>3</sub>/n-Si MOS devices after a 6 V constant voltage stress for 10 s. The  $V_{\rm fb}$  value kept almost unchanged during  $10^4$  s, as shown in Fig. S1, which means few electrons escaped from the traps. If electrons were trapped by the shallow traps, they would detrap from the shallow traps and the  $V_{\rm fb}$  would shift to the initial state. So, this suggests that electrons were trapped in deep level traps. For CTM applications, the high trap density in the charge-trapping layer is benefit for a large memory window, and fewer defects are necessary for tunneling and blocking layers.<sup>4</sup> It means that we can use the Al<sub>2</sub>O<sub>3</sub> layer as charge-trapping or blocking layers by manipulating the defects level through changing the oxygen sources of ALD Al<sub>2</sub>O<sub>3</sub> films.

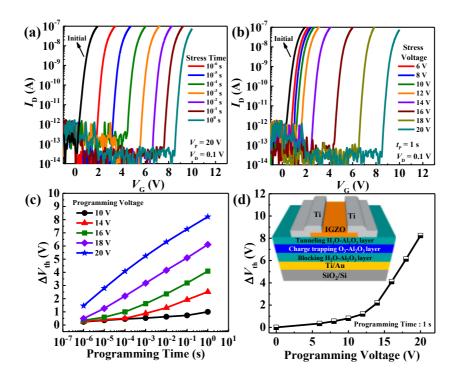

Based on above experimental results, IGZO CTM devices with homogeneous Al<sub>2</sub>O<sub>3</sub> gate stack have been fabricated, and the device structure is shown in the inset of Fig. 3(d). The densified H<sub>2</sub>O-Al<sub>2</sub>O<sub>3</sub> layers were used as blocking and tunneling layers, and the defect-rich O<sub>3</sub>-Al<sub>2</sub>O<sub>3</sub> film was chosen as the charge-trapping layer. To examine the memory properties of IGZO CTM devices,

program processes with different programming voltages ( $V_P$ ) and programming time ( $t_P$ ) were firstly investigated. During the program processes, the source and drain electrodes of the IGZO CTM devices were grounded, and a fixed stress voltage was applied on the gate electrode for different time. Fig. 3(a) shows the transfer characteristics of IGZO CTM after programming at 20 V with different  $t_P$  from 1  $\mu$ s to 1 s. A continuously parallel positive shift can be found from the transfer ( $I_D$ - $V_G$ ) curves without obvious accompanying degradation in subthreshold swing (SS). The threshold voltage shift ( $\Delta V_{th}$ ), which is also the memory window, as a function of  $t_P$  under different  $V_P$  was summarized in Fig. 3(c). The value of  $\Delta V_{th}$  greatly increased under large programming gate voltage and long programming time, which means that more electrons can get enough energy to tunnel into defect-rich charge-trapping O<sub>3</sub>-Al<sub>2</sub>O<sub>3</sub> layer. Fig. 3(b) shows the transfer curves of IGZO CTM after different  $V_P$  of 1 s. The relationship between  $\Delta V_{th}$  and programming voltage was summarized in Fig. 3(d).  $\Delta V_{th}$  is about 8.2 V at a programming voltage of +20 V for 1 s, indicating a good charge-storage capability of the IGZO CTM.

**Figure 3.** Transfer characteristics of IGZO CTM (a) after operation at 20 V with different  $t_P$ , and (b) after operation at 1s with different  $V_P$ . The "Initial" curve stands for the devices without program process.  $\Delta V_{th}$  as a function of the (c)  $t_P$  with different  $V_P$  and (d) different  $V_P$  with 1 s  $t_P$ . The inset is the structure image of IGZO CTM devices.

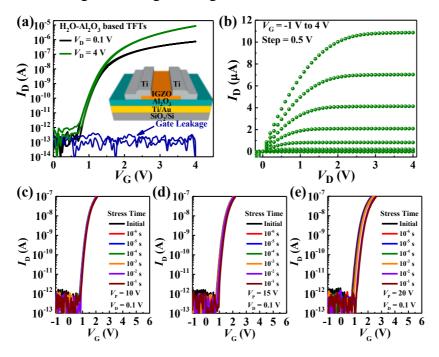

As the control samples, the program processes of IGZO TFTs based on 30 nm H<sub>2</sub>O-Al<sub>2</sub>O<sub>3</sub> film

were evaluated to further demonstrate the charge-trapping capability of  $O_3$ -Al<sub>2</sub>O<sub>3</sub>. The transfer and output characteristics of the controlled IGZO TFTs are shown in Figs. 4(a) and (b), respectively. The TFTs exhibit a well-defined pinch-off behaviour with a high saturation mobility ( $\mu_{sat}$  = 10.96 cm<sup>2</sup>/Vs), a small subthreshold swing (SS = 112 mV/dec), and a high on/off current ratio ( $I_{on}/I_{off}$  =  $8.6 \times 10^8$ ). The hysteresis of TFTs was extremely small and the leakage currents were suppressed well, which means that the H<sub>2</sub>O-Al<sub>2</sub>O<sub>3</sub> played good roles as an excellent gate dielectric layer. Figs. 4(c)-4(e) show the stress time dependence of IGZO TFTs transfer curves after operation at 10, 15, and 20 V stress voltages, respectively. There were almost no changes of transfer curves, when the stress voltages were 10 V and 15 V. Even under a large stress voltage of 20 V, the threshold voltage shift was only ~0.35 V, which can be neglected compared with 8.2 V memory window for O<sub>3</sub>-Al<sub>2</sub>O<sub>3</sub> CTM devices. Thus, the charge-storage capability of CTM devices was mainly benefited from the defect-rich O<sub>3</sub>-Al<sub>2</sub>O<sub>3</sub> among the homogeneous gate stacks.

**Figure 4.** (a) Transfer and (b) output characteristics of the IGZO TFTs. The stress time dependence of the IGZO TFTs after operation at (c) 10 V, (d) 15 V, and (e) 20 V stress voltages, respectively.

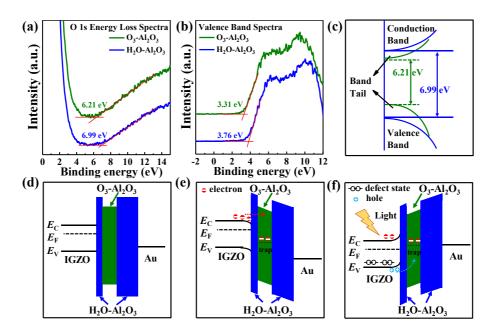

The energy band conditions of the Al<sub>2</sub>O<sub>3</sub> films were also investigated by XPS measurements. Fig. 5(a) shows the O 1s electron energy loss spectra from two types of Al<sub>2</sub>O<sub>3</sub> films. The values of energy gap were calculated to be 6.99 eV and 6.21 eV for H<sub>2</sub>O-Al<sub>2</sub>O<sub>3</sub> and O<sub>3</sub>-Al<sub>2</sub>O<sub>3</sub>, respectively. A band gap narrowing was happened in O<sub>3</sub>-Al<sub>2</sub>O<sub>3</sub> film, as shown in Fig. 5(c). The band edge of the carbon-related defects in the O<sub>3</sub>-Al<sub>2</sub>O<sub>3</sub> film may shift deep into the forbidden gap, which could form band tails gap and reduce the effective band gap of the film.<sup>31,32</sup> The valence band offset ( $\Delta E_V = 0.45 \text{ eV}$ ) of the Al<sub>2</sub>O<sub>3</sub> films was calculated from the valence band spectra, as shown in Fig. 5(b). Furthermore, the conduction band offset ( $\Delta E_C = 0.33 \text{ eV}$ ) can be derived by the equation of  $\Delta E_C = E_g(\text{H}_2\text{O}-\text{Al}_2\text{O}_3) - E_g(\text{O}_3-\text{Al}_2\text{O}_3) - \Delta E_V$ . The IGZO bandgap was reported about 3.0~3.3 eV.<sup>19</sup> Thus, we can get the energy band schematic diagrams of IGZO CTM devices in flat band and programming states, as shown in Fig. 5(d) and 5(e). For further improving the performances of CTM devices, such as faster programming speed, larger memory window, and better retention characteristics, the band engineering may be applied to our IGZO CTM devices.<sup>33-35</sup>

**Figure 5.** (a) O 1s electron energy loss spectra and (b) valence band spectra of Al<sub>2</sub>O<sub>3</sub> films. (c) Carbon-related defects induced band gap narrowing effects in O<sub>3</sub>-Al<sub>2</sub>O<sub>3</sub> film. Energy-band diagrams of IGZO CTM devices in (d) flat band state, (e) programming, and (f) erasing processes with light illumination.

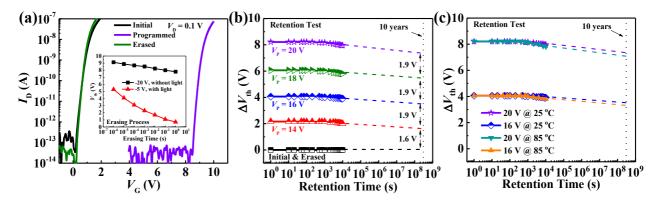

Erasing characteristics of the IGZO CTM were investigated after a  $+20 \text{ V} V_P$  for 1 s, as shown in Fig. 6(a). The erasing characteristics of the device programmed with different stress voltages are shown in Fig. S2(a). However, the n-type IGZO channel material only supplies electrons due to Fermi level pinning.<sup>36</sup> During the erasing process, even we applied a high negative gate voltage (-

20 V) on the devices, the  $V_{th}$  shift is not obvious, only 1.5 V  $\Delta V_{th}$  with 1 s stress, as shown in the inset of Fig. 6(a). Very few holes can be trapped into the charge-trapping O<sub>3</sub>-Al<sub>2</sub>O<sub>3</sub> layer under negative gate bias voltages. As such, a LED light source with the wavelength of 450~460 nm and power density of 3 mW/cm<sup>2</sup> was used during the erasing processes. Light erasing processes were also reported in a few other IGZO CTM devices. <sup>19,37,38</sup> It was reported that IGZO has some subgap defect states above the valence band maximum (VBM), holes can be generated under exposure to light with a photon energy (~2.3 eV, which is corresponding to ~540 nm). <sup>39,40</sup> So, as shown in Fig. 5(f), under light illumination, a large amount of electron-hole pairs may be excited in the IGZO channel by enough photons with sufficient energy, and some holes with enough energy could get through the tunneling layer and neutralize the trapped electrons in the O<sub>3</sub>-Al<sub>2</sub>O<sub>3</sub> layer. <sup>19,37,38</sup> Under light illumination, the memory device can be erased entirely under a small negative bias of -5 V for 100 ms. More efforts need to be done to achieve erasing step without light, such as modifying the energy level of the defects in the charge-trapping layer. <sup>34</sup>

**Figure 6.** (a) The comparison of erasing process with or without light condition. The multi-level storage retention characteristics of the IGZO CTM at (b) 25 °C and (c) 85 °C.

Fig. 6(b) shows the multi-level storage retention characteristics of the IGZO CTM devices at room temperature (25 °C). During the retention measurements, source, drain, and gate electrodes were all at zero biases after programmed by different stress voltages for 1 s. The threshold voltage kept almost unchanged for CTM devices without programming process and after erased to the initial states. The retention data of the programmed device after being partially erased with light is shown in Fig. S2(b). According to the trend of data showing by the dashed lines in Fig. 6(b), a large

memory window of 7.3 V after 10-year retention is deduced with a 0.9 V retention loss and about 11.0 % charge loss. Multi-level-storage states were also achieved in our IGZO CTM, which were programmed with 14, 16, 18, and 20 V different voltages, respectively. And a 1.9 V wide margin between the adjacent two states could be maintained for 10 years according to the trend of data. The retention characteristics at 85 °C are shown in Fig. 6(c). Comparing with the threshold voltage at 25 °C, there is only a ~0.3 V decrease after 10 years for the same programming state. The device performance showed a slight decay at a high temperature, which may be caused by the thermally activated charge detrapping. The good retention characteristics of the IGZO CTM devices may be attribute to the deep trapping levels of electrons in the O<sub>3</sub>-Al<sub>2</sub>O<sub>3</sub> charge-storage layer, which is benefit for realizing multi-level memory applications.

# 4. CONCLUSIONS

In summary, IGZO charge-trapping memory (CTM) was fabricated with a homogeneous triple-layer alumina dielectric grown by atomic-layer deposition consecutively at 150 °C temperature. By using different oxygen sources, the obtained Al<sub>2</sub>O<sub>3</sub> layers were shown to be capable of acting as the tunneling layer, the charge-trapping layer and the charge-blocking layer. The chemical constituents of the two types of Al<sub>2</sub>O<sub>3</sub> films have been analyzed by X-ray photoelectron spectroscopy, and the charge-trapping states in O<sub>3</sub>-Al<sub>2</sub>O<sub>3</sub> may be caused by the residual C-related oxidation states. A large memory window of 8.2 V was obtained by programming voltage of +20 V. And multi-level storage was achieved in our IGZO CTM after different programming voltages. The IGZO CTM devices may have promising potentials for multi-level-storage nonvolatile memory applications with the advantages of being based on thin-film technologies and having a simple structure for manufacturing.

# **AUTHOR INFORMATION**

Corresponding Authors

\*E-mail: A.Song@manchester.ac.uk

\*E-mail: yxli@sdu.edu.cn

ORCID:

Pengfei Ma: 0000-0003-1257-8021

Qian Xin: 0000–0003–4605–5894

Yuxiang Li: 0000-0002-9457-769X

Aimin Song: 0000-0001-6550-518X

Acknowledgements

This work was financed by the National Key Research and Development Program of China

(Grant Nos. 2016YFA0201800 and 2016YFA0301200), Engineering and Physical Sciences

Research Council (EPSRC) (Grant No. EP/N021258/1), China Postdoctoral Science Foundation

(2015M582073 and 2016M590634), the Key Research and Development Program of Shandong

Province (2017GGX10111), the Natural Science Foundation of Shandong Province

(ZR2013FM033 and ZR2018MF029), and the Fundamental Research Funds of Shandong

University (2016WLJH44).

REFERENCES

(1) Ding, P.; Yang, Y.; Wang, Y.; Liu, C.; Yin, J.; Xia, Y.; Li, A.; Liu, Z. Band-alignment dominated

retention behaviors in high-k composite charge-trapping memory devices. Appl. Phys. Lett.

**2019,** 114, 053506.

(2) Tanaka, H.; Kido, M.; Yahashi, K.; Oomura, M.; Katsumata, R.; Kito, M.; Fukuzumi, Y.; Sato,

M.; Nagata, Y.; Matsuoka, Y.; Iwata, Y.; Aochi, H.; Nitayama, A.; Japan Soc Appl, P. Bit cost

scalable technology with punch and plug process for ultra high density Flash memory. IEEE

Symp. VLSI Technol. 2007, 14-15.

(3) Park, K.-T.; Nam, S.; Kim, D.; Kwak, P.; Lee, D.; Choi, Y.-H.; Choi, M.-H.; Kwak, D.-H.; Kim,

D.-H.; Kim, M.-S.; Park, H.-W.; Shim, S.-W.; Kang, K.-M.; Park, S.-W.; Lee, K.; Yoon, H.-J.;

Ko, K.; Shim, D.-K.; Ahn, Y.-L.; Ryu, J.; Kim, D.; Yun, K.; Kwon, J.; Shin, S.; Byeon, D.-S.;

Choi, K.; Han, J.-M.; Kyung, K.-H.; Choi, J.-H.; Kim, K. Three-Dimensional 128 Gb MLC

13

- Vertical NAND Flash Memory With 24-WL Stacked Layers and 50 MB/s High-Speed Programming. *IEEE J. Solid-State Circuits* **2015**, *50*, 204-213.

- (4) Tan, C. L.; Lavizzari, S.; Blomme, P.; Breuil, L.; Vecchio, G.; Sebaai, F.; Paraschiv, V.; Tao, Z.; Schepers, B.; Nyns, L.; Peter, A.; Dekkers, H.; Ong, P.; Tsvetanova, D.; Devriendt, K.; Teugels, L.; Heylen, N.; Raymaekers, T.; Jossart, N.; Mennella, P.; Delhougne, R.; V-Palayam, S. S.; Arreghini, A.; Van den bosch, G.; Furnemont, A. In depth analysis of 3D NAND enablers in gate stack integration and demonstration in 3D devices. *IMW* **2017**, 1-4.

- (5) Ma, P.; Guo, W.; Sun, J.; Gao, J.; Zhang, G.; Xin, Q.; Li, Y.; Song, A. Electron transport mechanism through ultrathin Al<sub>2</sub>O<sub>3</sub> films grown at low temperatures using atomic–layer deposition. *Semicond. Sci. Technol.* **2019**, *34*, 105004.

- (6) Ma, P.; Du, L.; Wang, Y.; Jiang, R.; Xin, Q.; Li, Y.; Song, A. Low voltage operation of IGZO thin film transistors enabled by ultrathin Al<sub>2</sub>O<sub>3</sub> gate dielectric. *Appl. Phys. Lett.* **2018**, *112*, 023501.

- (7) Xi, K.; Bi, J. S.; Hu, Y.; Li, B.; Liu, J.; Xu, Y. N.; Liu, M. Impact of gamma-ray irradiation on graphene nano-disc non-volatile memory. *Appl. Phys. Lett.* **2018**, *113*, 164103

- (8) Han, P.; Lai, T.-C.; Wang, M.; Zhao, X.-R.; Cao, Y.-Q.; Wu, D.; Li, A.-D. Outstanding memory characteristics with atomic layer deposited Ta<sub>2</sub>O<sub>5</sub>/Al<sub>2</sub>O<sub>3</sub>/TiO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>/Ta<sub>2</sub>O<sub>5</sub> nanocomposite structures as the charge trapping layer. *Appl. Surf. Sci.* **2019**, *467*, 423-427.

- (9) Zhang, W.; Liang, R.; Liu, L.; Yu, G.; Wang, J.; Xu, J.; Ren, T.-L. Demonstration of alpha-InGaZnO TFT nonvolatile memory using TiAlO charge trapping layer. *IEEE Transactions on Nanotechnology* **2018**, *17*, 1089-1093.

- (10) Spassov, D.; Skeparovski, A.; Paskaleva, A.; Novkovski, N. A comparative study of charge trapping in HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> and ZrO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> based multilayered metal/high-k/oxide/Si structures. *Thin Solid Films* **2016**, *614*, 7-15.

- (11) Jin, H. S.; Kim, D. H.; Kim, S. K.; Wallace, R. M.; Kim, J.; Park, T. J. Strategic selection of the oxygen source for low temperature-atomic layer deposition of Al<sub>2</sub>O<sub>3</sub> thin film. *Adv. Electron. Mater.* **2018**, *5*, 1800680.

- (12) Seo, S.; Nam, T.; Lee, H.-B.-R.; Kim, H.; Shong, B. Molecular oxidation of surface –CH<sub>3</sub> during atomic layer deposition of Al<sub>2</sub>O<sub>3</sub> with H<sub>2</sub>O, H<sub>2</sub>O<sub>2</sub>, and O<sub>3</sub>: A theoretical study. *Appl. Surf. Sci.* **2018**, *457*, 376-380.

- (13) Nitayama, A.; Aochi, H. Vertical 3D NAND Flash Memory Technology. *ECS Trans.* **2011,** *41*, 15-25.

- (14) Choi, E.-S.; Park, S.-K.; Ieee Device Considerations for High Density and Highly Reliable 3D NAND Flash Cell in Near Future. *IEDM* **2012**, 211-214.

- (15) Degraeve, R.; Toledano-Luque, M.; Suhane, A.; Van den Bosch, G.; Arreghini, A.; Tang, B.; Kaczer, B.; Roussel, P.; Kar, G. S.; Van Houdt, J.; Groeseneken, G. Statistical characterization of current paths in narrow poly-Si channels. *IEDM* **2011**, 287-290.

- (16) Nomura, K.; Ohta, H.; Takagi, A.; Kamiya, T.; Hirano, M.; Hosono, H. Room-Temperature Fabrication of Transparent Flexible Thin-Film Transistors Using Amorphous Oxide Semiconductors. *Nature* **2004**, *432*, 488-492.

- (17) Ma, P.; Sun, J.; Zhang, G.; Liang, G.; Xin, Q.; Li, Y.; Song, A. Low-temperature fabrication of HfAlO alloy dielectric using atomic-layer deposition and its application in a low-power device. *J. Alloys Compd.* **2019**, *792*, 543-549.

- (18) Ma, P.; Sun, J.; Liang, G.; Li, Y.; Xin, Q.; Li, Y.; Song, A. Half-volt Operation of IGZO Thin-Film Transistors Enabled by Ultrathin HfO<sub>2</sub> Gate Dielectric. *Appl. Phys. Lett.* **2018**, *113*, 063501.

- (19) Thuy Trinh, T.; Duy Nguyen, V.; Hanh Nguyen, H.; Raja, J.; Jang, J.; Jang, K.; Baek, K.; Ai Dao, V.; Yi, J. Operation Mechanism of Schottky Barrier Nonvolatile Memory with High Conductivity InGaZnO Active Layer. *Appl. Phys. Lett.* **2012**, *100*, 143502.

- (20) Hwang, E. S.; Kim, J. S.; Jeon, S. M.; Lee, S. J.; Jang, Y.; Cho, D.-Y.; Hwang, C. S. ln<sub>2</sub>Ga<sub>2</sub>ZnO<sub>7</sub> oxide semiconductor based charge trap device for NAND flash memory. *Nanotechnology* **2018**, *29*, 155203.

- (21) Yun, D.-J.; Kang, H.-B.; Yoon, S.-M. Process Optimization and Device Characterization of Nonvolatile Charge Trap Memory Transistors Using In-Ga-ZnO Thin Films as Both Charge Trap and Active Channel Layers. *IEEE Trans. Electron Devices* **2016**, *63*, 3128-3134.

- (22) Pan, T.-M.; Chen, C.-H.; Hu, Y.-H.; Wang, H.-C.; Her, J.-L. Comparison of structural and electrical properties of Er<sub>2</sub>O<sub>3</sub> and ErTi<sub>x</sub>O<sub>y</sub> charge-trapping layers for InGaZnO thin-film transistor nonvolatile memory Devices. *IEEE Electron Device Lett.* **2016**, *37*, 179-181.

- (23) Pan, T.-M.; Chen, C.-H.; Hu, Y.-H.; Her, J.-L. Effect of Ti Content on the Structural and Electrical Characteristics of ErTi<sub>x</sub>O<sub>y</sub> Charge Storage Layer in InGaZnO Thin-Film Transistor Nonvolatile Memories. *IEEE Trans. Electron Devices* **2016**, *63*, 1539-1544.

- (24) Ahn, M.-J.; Cho, W.-J. Transparent multi-level-cell nonvolatile memory with dual-gate amorphous indium-gallium-zinc oxide thin-film transistors. *Appl. Phys. Lett.* **2016**, *109*, 252106.

- (25) Yoon, S.-M.; Seong, N.-J.; Choi, K.; Seo, G.-H.; Shin, W.-C. Effects of Deposition Temperature on the Device Characteristics of Oxide Thin-Film Transistors Using In-Ga-Zn-O Active Channels Prepared by Atomic-Layer Deposition. *ACS Appl. Mater. Interfaces* **2017**, *9*, 22676-22684.

- (26) Seong Keun, K.; Suk Woo, L.; Cheol Seong, H.; Yo-Sep, M.; Jeong Yeon, W.; Jaehack, J. Low temperature (<100degC) deposition of aluminum oxide thin films by ALD with O3 as oxidant. *J. Electrochem. Soc.* **2006**, *153*, F69-76.

- (27) Kim, J.; Chakrabarti, K.; Lee, J.; Oh, K. Y.; Lee, C. Effects of ozone as an oxygen source on the properties of the Al2O3 thin films prepared by atomic layer deposition. *Mater. Chem. Phys.* **2003**, *78*, 733-738.

- (28) Goldstein, D. N.; McCormick, J. A.; George, S. M. Al2O3 Atomic Layer Deposition with Trimethylaluminum and Ozone Studied by in Situ Transmission FTIR Spectroscopy and Quadrupole Mass Spectrometry. *The Journal of Physical Chemistry C* **2008**, *112*, 19530-19539.

- (29) Elliott, S. D.; Scarel, G.; Wiemer, C.; Fanciulli, M.; Pavia, G. Ozone-based atomic layer deposition of alumina from TMA: Growth, morphology, and reaction mechanism. *Chem. Mater.* **2006**, *18*, 3764-3773.

- (30) Gao, J.; He, G.; Zhang, J.; Chen, X.; Jin, P.; Xiao, D.; Liu, M.; Ma, R.; Sun, Z. Annealing Temperature Dependent Electrical Properties and Leakage Current Transport Mechanisms in Atomic Layer Deposition-Derived Al<sub>2</sub>O<sub>3</sub>-Incorporated HfO<sub>2</sub>/Si Gate Stack. *J. Nanosci. Nanotechnol.* **2016**, *16*, 8075-8082.

- (31) O'Reilly, E. P.; Robertson, J. Theory of defects in vitreous silicon dioxide. *Phys. Rev. B* **1983**, 27, 3780-3795.

- (32) Guo, X.; Zheng, H.; King, S. W.; Afanas'ev, V. V.; Baklanov, M. R.; de Marneffe, J. F.; Nishi, Y.; Shohet, J. L. Defect-induced bandgap narrowing in low-k dielectrics. *Appl. Phys. Lett.* **2015**, *107*, 082903.

- (33) Yan, C.; Wen, J.; Lin, P.; Sun, Z. A tunneling dielectric layer free floating gate nonvolatile memory employing type-I core-shell quantum dots as discrete charge-trapping/tunneling centers. *Small* **2019**, *15*, 1804156.

- (34) Breuil, L.; Lisoni, J. G.; Blomme, P.; Van den Bosch, G.; Van Houdt, J. HfO<sub>2</sub> Based High-k Inter-Gate Dielectrics for Planar NAND Flash Memory. *IEEE Electron Device Lett.* **2014**, *35*, 45-47.

- (35) Hota, M. K.; Alshammari, F. H.; Salama, K. N.; Alshareef, H. N. Transparent Flash memory using single Ta<sub>2</sub>O<sub>5</sub> layer for both charge-trapping and tunneling dielectrics. *ACS Appl. Mater. Interfaces* **2017**, *9*, 21856-21863.

- (36) Lee, S. Y.; Kim, D. H.; Chong, E.; Jeon, Y. W.; Kim, D. H. Effect of channel thickness on density of states in amorphous InGaZnO thin film transistor. *Appl. Phys. Lett.* **2011**, *98*, 122105.

- (37) Chen, S.; Zhang, W.-P.; Cui, X.-M.; Ding, S.-J.; Sun, Q.-Q.; Zhang, W. Monochromatic light-assisted erasing effects of In-Ga-Zn-O thin film transistor memory with Al<sub>2</sub>O<sub>3</sub>/Zn-doped Al<sub>2</sub>O<sub>3</sub>/Al<sub>2</sub>O<sub>3</sub> stacks. *Appl. Phys. Lett.* **2014**, *104*, 103504.

- (38) Chen, S.; Cui, X.-M.; Ding, S.-J.; Sun, Q.-Q.; Nyberg, T.; Zhang, S.-L.; Zhang, W. Novel Zn-Doped Al<sub>2</sub>O<sub>3</sub> Charge Storage Medium for Light-Erasable In–Ga–Zn–O TFT Memory. *IEEE Electron Device Lett.* **2013**, *34*, 1008-1010.

- (39) Nomura, K.; Kamiya, T.; Ikenaga, E.; Yanagi, H.; Kobayashi, K.; Hosono, H. Depth analysis of subgap electronic states in amorphous oxide semiconductor, a-In-Ga-Zn-O, studied by hard x-ray photoelectron spectroscopy. *J. Appl. Phys.* **2011**, *109*, 073726.

- (40) Jung, H.; Kim, W.-H.; Park, B.-E.; Woo, W. J.; Oh, I.-K.; Lee, S. J.; Kim, Y. C.; Myoung, J.-M.; Gatineau, S.; Dussarrat, C.; Kim, H. Enhanced Light Stability of InGaZnO Thin-Film Transistors by Atomic-Layer-Deposited Y<sub>2</sub>O<sub>3</sub> with Ozone. *ACS Appl. Mater. Interfaces* **2018**, *10*, 2143-2150.